Image Credit: Getty Images

Did you miss a session from the Future of Work Summit? Head over to our Future of Work Summit on-demand library to stream.

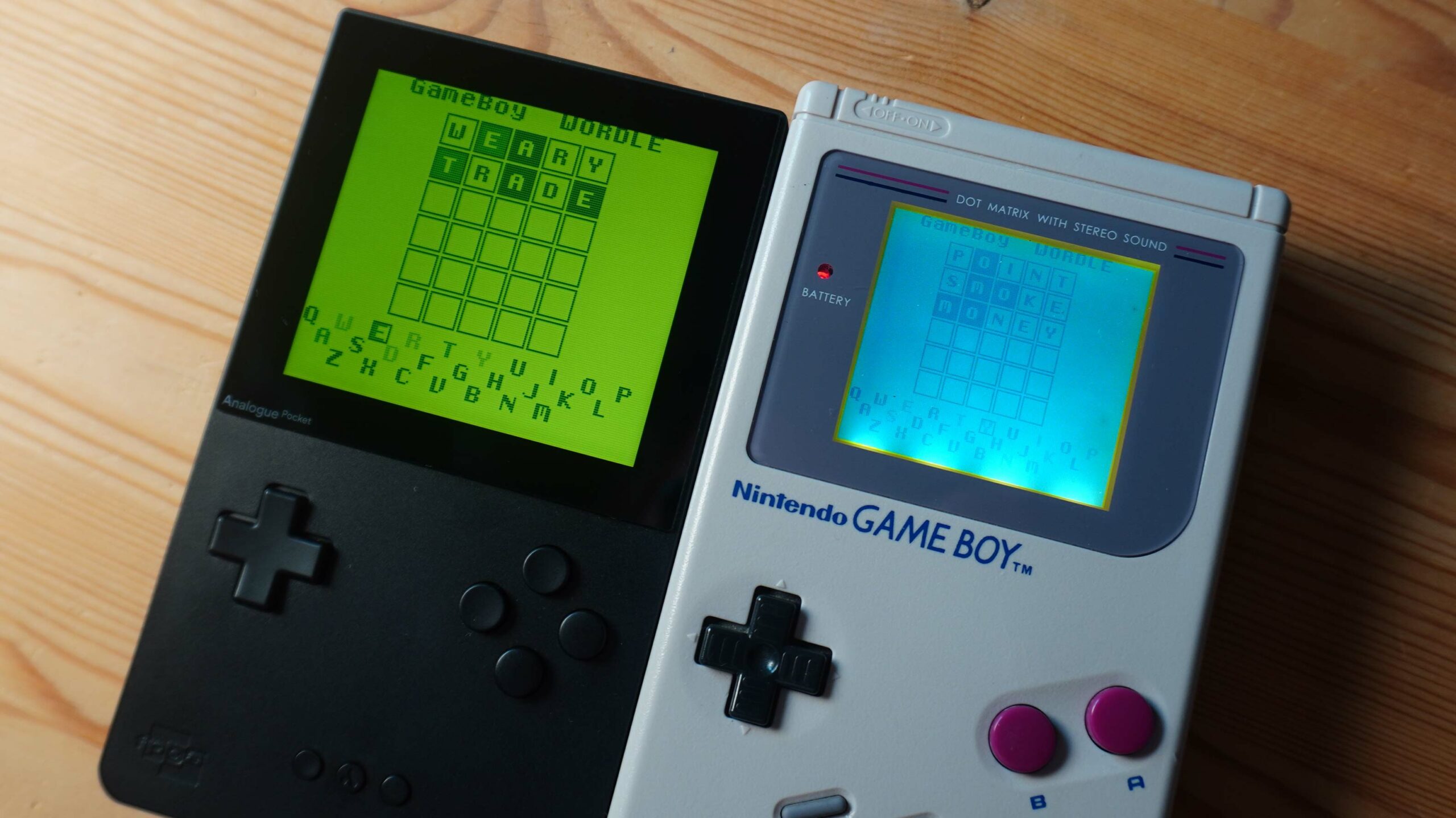

At the 2021 IEEE International Electron Devices Meeting (IEDM), Intel demonstrated for the first time a functional MESO (Magneto-Electric Spin-Orbit) transistor. MESO is what’s called a “beyond-CMOS” device. That is, it represents a fundamental new way of building a transistor (and hence computers) and uses room-temperature quantum materials. MESO could be 10 to 30 times more efficient than existing transistors and could help spur AI efforts across a variety of industries.

Although still in the research phase, MESO would represent the biggest advance in computing since the introduction of the transistor, if it reaches commercialization, and would likely lead to revisions in electrical engineering courses and textbooks. Intel’s prior theoretical research had shown that MESO could offer significant advances over conventional transistors in the energy consumption and chip area. MESO could allow circuits to run at just 100mV, and would be especially promising for application in AI chips.

In the more recent demonstration, Intel showed the potential of the new transistor.

In 2021, Intel laid out its process roadmap through 2025, which it will also use to build its new Intel Foundry Service business. Most noteworthy from that roadmap is that, in 2024, Intel will make another big (but more evolutionary) change to the transistor with the introduction of RibbonFET and PowerVia.

Although MESO remains a future technology, it’s significant because it’s the first transistor (out of dozens of alternatives that have been researched) that may be capable of replacing – or at least augmenting – conventional semiconductors. The next few sections will dive into the physics behind MESO.

How MESO goes beyond CMOS

Although computing existed well before the invention of transistors (through devices such as vacuum tubes), it’s only been since the transistor that computing has started to advance exponentially. The continued miniaturization of these devices has led to a trend widely known as Moore’s Law. Besides the fact that transistors lend themselves to scaling, what fundamentally makes them so successful is that they provide circuit designers with an on-off switch that also provides a gain. Furthermore, transistor fabrication is based on silicon, which is a semiconductor whose properties can be controlled through doping. That is, its conductivity can be precisely determined by inserting (doping) silicon with impurities.

Through the years, especially as the transistor started to enter nanoscale dimensions, it has already seen many enhancements to improve speed, or to reduce power consumption or leakage. One of the biggest of these improvements was to change the transistor from a planar device to a 3D FinFET (where the fin extends out of the initial silicon wafer). In the next several years, this structure will be further improved by the gate-all-around transistor, which goes by various names such as the RibbonFET (Intel) or MCBFET (Samsung).

However, despite these changes, the architecture of a MOSFET has fundamentally remained the same: the current through the channel of the transistor is controlled by applying a voltage to the gate. The gate itself is insulated from the conducting channel, so current only flows from input to output. The input and output contacts are known as the source and drain.

Over time, various alternative structures have been proposed. These seek to accomplish the same on-off switch characteristics as a MOSFET, but based on other physical properties and mechanisms.

From that view, the MOSFET can be classified as a charge-based, electronic device: its working is based on electronic (electrostatic) properties. Also in the charge-based category, another device that has been researched is the tunnel FET, which uses the quantum mechanical property of tunneling. Other device types include orbitronics, magneto-electronics, and spintronics.

Are these kinds of devices are just curiosities for physicists and engineers to research or are some of these are capable of replacing silicon in high-volume manufacturing. The answer relies on the fundamental working principles of semiconductors, which impose a fundamental limit.

Remember that as an on-off switch to function properly one needs to obtain a significant difference in current between the on- and off-states. As mentioned above, this is controlled by applying a voltage to the gate. However, the current through a transistor doesn’t change arbitrarily when a voltage is applied. Ultimately, a semiconductor is limited by the laws of statistics and thermodynamics: given the thermal energy available to electrons at room temperature, there is a fundamental limit to how much the current through a transistor can decrease as the voltage is decreased.

More specifically, the laws of thermodynamics impose a distribution in the energy available to electrons at a given temperature (since temperature by definition refers only to their average energy). The “tail” of this distribution decays exponentially. So when the transistor is turned off (reducing the voltage below the threshold), current will decrease exponentially as voltage is decreased. Crucially, the exact rate of this decay also depends on temperature.

This property is known as the subthreshold slope, and it’s expressed in terms of how many millivolts are required to increase or decrease the current by 10x. (The exact limit is ~60mV/dec, as it turns out.) It’s this slope that determines the minimum operating voltage of a transistor. A transistor with a steeper slope would be able to operate at a lower voltage, which would reduce its power consumption and thus result in a higher energy efficiency and speed. But since this slope is purely determined by thermodynamics, the only way to make the slope steeper would be to decrease the temperature, which of course is unfeasible. This limitation is also known as the Boltzmann tyranny.

Because the switching characteristics of a conventional CMOS device are determined (and limited) by fundamental physics, the only way to possibly circumvent this barrier is to look for devices that operate based on different physical mechanisms. This is where the appeal for beyond-CMOS devices comes from.

Although a large amount of alternatives to the conventional transistor have been proposed, decades of R&D in silicon have made silicon a tough material to beat. In a landmark research paper in 2017, Intel benchmarked about two dozen beyond-CMOS devices. As can be seen from the summary graph, hardly any device is faster than HP CMOS, and just a few are lower power than LP CMOS. But overall, there didn’t seem to be any one candidate that is both faster and at a lower power. Without substantial improvements over CMOS, it is doubtful that it would be worthwhile to spend billions of dollars of R&D to make such a new switch suitable for high-volume manufacturing, as other issues such as cost might also come into play.

So given the versatility of CMOS and regular semiconductors from low power to high performance, and from analog to RF to high voltage to digital, it is unlikely that current CMOS technology will ever be fully replaced. Rather, a new technology would perhaps be integrated in combination with CMOS so that it could be used only for the circuits in a system where it delivers a real benefit.

How MESO goes beyond CMOS

More recently, a new kind of device (MESO) has emerged, invented by Intel and proposed in a 2018 paper. Intel claimed it has the potential to deliver substantial benefits compared to CMOS. Since it would operate at just 100mV, it could result in 10 to 30 times higher efficiency. Intel further claimed it could improve logic density by 5x. The MESO device is also non-volatile (which means its state is conserved when power is turned off) and has spintronic properties, which means new kinds of circuits could be implemented, suitable for AI.

“MESO is like a transistor – input voltage controls the current at the output (so it is electrical voltage in and current out like MOSFETs, but it switches at 10x lower voltage than a MOSFET,” according to Intel. “Thus, wires only have top swing 10X lower voltage – this saves power.”

However, while similar to a transistor, the architecture and physics of the MESO transistor completely differs from conventional semiconductors, as it makes heavy use of quantum effects and materials. Referring to the beyond-CMOS classification above, MESO makes use of no less than three classes of information carriers: electronics, magneto-electronics, and spintronics.

However, perhaps the most elegant aspect about MESO is that all complexity is restricted to the device itself: Information comes into the device through a conventional charge-based interconnect, and at the end leaves the device again as an electrical current. In the device itself, the charge is first converted to magnetism using the magneto-electric effect, and then converted back to charge using the spin-orbit effect. The device and information flow is shown in the image below.

In more detail, the device architecture works as follows. The input is a ferroelectric capacitor that is connected to a regular charge-based interconnect. Ferroelectric materials are materials whose magnetic properties can be controlled through currents, which explains how charge is converted to magnetism. (Analogously, in an electric motor, ferroelectric materials can be used to convert current into motion through magnetism.) This ferroelectric material in turn controls a nanomagnet or ferromagnet, which will point north or south depending on its input.

Although this nanomagnet represents the output state of the transistor, it still has to be converted back to a current. This is achieved through a quantum effect called a spin-orbit interaction, or, more specifically, the inverse Rashba-Edelstein effect. In general, a spin-orbit interaction refers to the interaction of an electron with a magnetic field (recall from quantum physics that an electron has an intrinsic magnetic moment called its spin). A more technical description is that it is “a relativistic interaction of a particle’s spin with its motion inside a potential”. The Rashba-Edelstein effect is a mechanism to convert charge to spin, so the inverse effect accomplishes the desired conversion from spin to charge. As a current (Isupply in the image above) is sent through the nanomagnet, due to the inverse Rashba-Edelstein effect, the output will be a positive or negative current depending on the direction of the nanomagnet.

The switching property is obtained since the nanomagnet has a thresholding property: an input voltage controls the nanomagnet (through the ferroelectric material), which will point either north or south, which will then result in either a positive or a negative output current.

To make circuits with these devices then simply becomes a matter of connecting the output of one device to the input of the next device. For example, a positive output current in the first device would charge the ferroelectric input capacitor of the second device, while a negative current would discharge it. Interestingly, the thresholding property can also be used to build “majority gates” by using multiple voltages as input. As the name implies, a majority gate will output a 1 if the majority of its inputs is a 1. This is likely why Intel claimed the 5x density improvement: from the study of the broa der field of spintronics it has been known already that circuits built using majority gates could be much smaller (require much less transistors) than conventional CMOS circuits.

In summary, the input charge is converted to a magnetic “signal” through the ferroelectric material, which controls a nanomagnet. This nanomagnet in turn will determine the output charge based on a quantum effect that converts spin (induced by the nanomagnet) into charge. In the analogy with an electric motor, it is as if the input current controls the electric motor, which is at the same is used as an electric generator to convert the motion back into electricity (like in a wind turbine).

The room temperature quantum materials, which Intel highlighted in 2018 as the main hurdles toward the physical realization of this device, are “correlated oxides” and “topological states of matter.”

In the broader context of beyond-CMOS devices, since traditional electronics are based on charge instead of spin/magnetism, MESO solves the fundamental problem of the readout of the device due to conversion back to charge at the output. From the 2018 paper: “The discovery of strong spin –charge coupling in topological matter via a Rashba–Edelstein or topological two-dimensional electron gas enables this proposal for a charge-driven, scalable logic computing device.” For comparison, in traditional spintronics, the spin for example decays exponentially through an interconnect.

In more technical terms, the use of spin for the transistor is referred to as a “collective state switch” whose output is dependent on a “collective order parameter” that can have two values (plus or minus theta), which in practice just refers to the spin being up or down. Since there are two possible outputs, this is indeed a switch, but the different mechanism (based on the order parameter) that it used overcomes the Boltzmann tyranny that plagues traditional electronics.

The graph above shows Intel’s benchmark results (based on simulation) from 2018 for a 32-bit ALU. MESO achieved higher throughput density (TOPS per cm2) at a much lower power density than both CMOS HP and LV.

Besides the lower operating voltage, Intel indicated that the different transistor architecture also allows for improvements in the interconnect, with resistance and capacitance requirements that are up to 100x “less stringent than conventional interconnects,” which in turn would reduce interconnect power by 10x. This might also contribute to MESO’s efficiency, since interconnects in modern chips could consume over 50% of the total power. Furthermore, Intel has demonstrated that the MESO device characteristics improve as the device is scaled further down (following a cubic trend), and MESO also promises integration and compatibility with CMOS.

Intel’s original paper included various target specifications to reach a 1aJ/bit device. Intel claims this is 30x lower than CMOS, which seems in the ballpark given that another source provides a lower limit of ~144aJ/bit in older 45nm process technology. Although 1aJ/bit was provided as the target, further in the paper estimates from 0.1 to 10 aJ/bit were also mentioned.

How these device specifications would translate into chip-scale specifications with circuits running at perhaps GHz-scale frequencies (if that is even feasible with MESO) still remains to be seen. For comparison, state of the art commercial NPUs (neural processing units) achieve up to 10 TOPS/W at INT8 precision, which translates into 100 fJ/instruction or roughly 10 fJ/bit. This implies the circuit level is ~100x less efficient than a single inverter at its most efficient voltage-frequency operating point.

Applications in AI

In an interview with VentureBeat in 2019, Intel identified AI, in particular, as a promising application for the MESO device, rather than CPUs. This is based on a few reasons.

First, given the low operating voltage of the MESO device, it may not match the high frequencies of CMOS circuits. Rather, MESO might be most suitable for applications such as AI and graphics that rely on highly parallel operations that individually run at a lower speed than a CPU.

Secondly, AI can make use of the different switching properties of MESO. Deep learning, in particular, is suited to the majority gates that can be made with MESO. So by designing circuits to take advantage of majority gates, neural networks could be implemented with much less transistors: “Majority gates is the next door neighbor to the neuron. Deep neural networks is about neurons and weights. We’ve found that this MESO technology and things that can do majority gates is very attractive in AI,” Intel said. “With the MESO magnet, multiple inputs can be brought in through a ‘majority gate,’ or thresholding gate. This is analogous to how neural networks use weights to represent the influence of nodes.”

There could also be a more practical reason: “CPUs, which are the most commonplace when you’re building silicon, are oddly enough the hardest thing to build,” Amir Khosrowshahi, VP of Intel, said in the interview with VentureBeat. “But in AI, it’s a simpler architecture. AI has regular patterns, it’s mostly compute and interconnect, and memories. Also, neural networks are very tolerant to inhomogeneities in the substrate itself. So I feel this type of technology will be adopted sooner than expected in the AI space. By 2025, it’s going to be the biggest thing.”

Timeline for MESO

As for the commercialization of MESO, the 2025 timeline might be ambitious given how many challenges are involved with bringing a fundamentally new technology into production. For example, even improvements to standard transistors have often taken over a decade to go into production.

Based on the discussion above, there are two options. Either MESO could represent an alternative manufacturing technology that would be used alongside conventional CMOS circuits, or it could be targeted to succeed CMOS altogether, just like how the FinFET completely replaced the conventional planar transistor at the leading edge. Notably, a key reason for MESO to usurp CMOS is its substantial uptick in power efficiency, according to Intel. Because MESO requires MOSFETs for clocking and power gating of its driving current, it doesn’t need a DC current to operate. Therefore, with a lower power voltage, MESO will have a lower power dissipation when compared to CMOS, Intel claims.

In the former case, Intel could for example make chiplets using MESO transistors that would be attached to regular CMOS chiplets. This would be similar to how Intel also has distinct fabs for silicon photonics (which uses older process technology) or its 3D XPoint memory.

In the latter case, Intel already laid out its multi-year roadmap earlier this year, making it unlikely MESO will be commercialized this decade. According to this roadmap, Intel would introduce the 18A node in 2025, which would be the first to use the next-gen (over $300 million) high-NA EUV lithography tool from ASML. It would be the successor of 20A, where Intel plans to introduce the RibbonFET and PowerVia.

RibbonFET represents the biggest change to the transistor since the 3D FinFET in 2012, but it would still be more of an evolutionary change. RibbonFET extends the FinFET by wrapping the gate fully around the transistor, instead of just three sides with a fin. In addition, multiple ribbons (which together form one transistor) can be stacked vertically, reducing the area per transistor (and thus advancing Moore’s Law). Secondly, PowerVia represents Intel’s implementation of a backside power delivery network. This means the power delivery of the transistor would occur from below the chip, while the regular interconnections between transistors would remain above the transistors.

So if the length that the FinFET has been in use is any indication, Intel would most likely further develop the RibbonFET for several more generations before it might become required to introduce a new technology in order to keep up with Moore’s Law. For example, Intel has already demonstrated stacking both the PMOS and NMOS RibbonFETs on top of each other. This by itself could nearly double transistor density.

With MESO’s current iteration, however, it appears that Intel intends for MESO and CMOS to “coexist on the same chip.” In this complementary relationship, MESO is meant to oversee and improve the efficiency of energy-demanding workloads, whereas CMOS would focus on bolstering operations that require high speed, such as clocking and analog circuits. As of now, “MESO is an add-on to a CMOS process flow and is not included in the definition of a standard CMOS generation,” Intel said. “It can be added to any CMOS generation and provide a scalable energy efficiency improvement.”

First experimental realization

At IEDM 2021, in collaboration with several academia, Intel presented the first experimental realization of the MESO device, which brings it one step closer to commercialization.

It also provides some more insight into the materials that were used. As input, the magneto-electric layer consists of bismuth ferrite (BiFeO3), which is a perovskite oxide. The magnet is a “nanostructured CoFe element,” and the output is a Pt element.

The biggest challenge to make the MESO device a reality has been the conversion back to charge. In order for the circuit to work, the readout has to operate at the same voltage as the write operation. However, as detailed in a 2020 paper, the readout only worked at 10nV, but had since been improved to 100uV.

In the future, Intel intends to continue improving upon this voltage readout. At IEDM, the company claimed that it had found a tentative means to achieve “100mV input voltage switching (with thinner multiferric oxide BiFeO3 and its doping) and 100mV output voltage driving of capacitive load (with better quantum materials such as topological materials, 2D electron gases, and functional oxides).”

“Further scaling of the MESO device to 10s of nanometers and fabrication of circuits with MESO will then follow,” Intel said.

Other developments

IEDM as a research-oriented engineering conference gives a glimpse of the future, and Intel presented several more papers.

The most significant one, besides MESO, was about a chip packaging technology called hybrid bonding: Intel has already announced it would use this technology going forward and called it Foveros Direct. Foveros is the name of Intel’s family of 3D packaging technologies. Intel’s regular Foveros uses copper bumps with pitches of 35-45um. By contrast, hybrid bonding shrinks this down to 10um, and below. For example, TSMC has also developed hybrid bonding (and will be used in upcoming AMD CPUs), and has suggested it could continue to shrink further for the next decades. The benefit is a higher density of interconnections.

Moving beyond CMOS

In nanotechnology, there are two approaches to improve electronics. First, most R&D goes into developing the next generations of conventional electronics, which results in incremental improvements to continue Moore’s Law. Since Moore’s Law is an exponential trend, this has been successful. But alternatively, researchers have and are also investigating a wide array of so-called beyond-CMOS devices with different properties, based on other physical mechanisms. The primary reason to consider these alternative device architectures is to circumvent the “Boltzmann tyranny” that bottlenecks classical electronics, in order to drastically improve energy efficiency of computing.

In the last few years, MESO has become a frontrunner in this research. Its appeal arises from its architecture that uses a traditional electronic input and output, but with a conversion to magnetism, and then back to charge, that takes place in the device itself. Furthermore, as a spintronic device, MESO can be used to build majority gates. This could make it especially suitable for applications in AI, since fewer transistors would be required to create such circuits compared to standard CMOS. Combined with its low operating voltage of potentially just 100mV, MESO could deliver a step-size improvement in energy efficiency.

To that end, Intel’s recent demonstration of the first experimental realization of this device shows that it continues to make progress to turn this into a technology that might one day replace, or at least augment, CMOS as the state-of-the-art of process technology.

VentureBeat

VentureBeat’s mission is to be a digital town square for technical decision-makers to gain knowledge about transformative technology and transact.Our site delivers essential information on data technologies and strategies to guide you as you lead your organizations. We invite you to become a member of our community, to access:

- up-to-date information on the subjects of interest to you

- our newsletters

- gated thought-leader content and discounted access to our prized events, such as Transform 2021: Learn More

- networking features, and more

Note: This article have been indexed to our site. We do not claim legitimacy, ownership or copyright of any of the content above. To see the article at original source Click Here